本征增益:MOS管的“性能天花板”

在模拟集成电路中,MOS管的本征增益(gm·ro)是衡量其放大能力的核心指标。它由跨导(gm)与输出电阻(ro)的乘积决定,直接决定了共源极放大器的低频增益上限。以.18μm工艺的NMOS为例,其本征增益通常在20-30dB区间,这一数值看似不高,却是所有负载配置的“理论天花板”。

工艺尺寸与增益的“博弈”

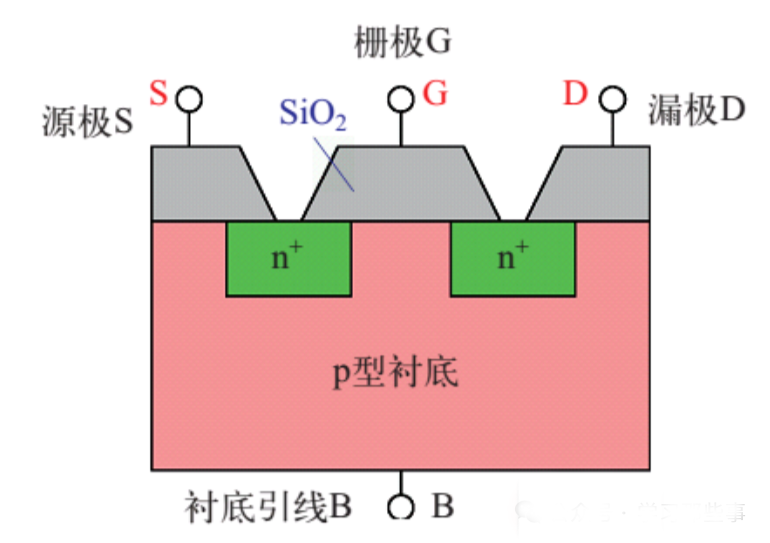

本征增益与沟道长度(L)呈正相关,与过驱动电压(VOD)呈反比。当工艺尺寸从微米级缩至深亚微米(如28nm以下),沟道长度调制效应加剧,导致输出电阻(ro)骤降,本征增益随之跌破10dB。这一趋势迫使设计师在增益与速度间寻找平衡:增大L可提升增益,但会降低工作频率;降低VOD虽能提高增益,却会牺牲动态响应。

负载配置:突破本征增益的“钥匙”

实际电路中,本征增益需通过负载配置“兑现”。电阻负载因与ro分压,实际增益仅为gm·ro的几分之一;电流源负载通过模拟无穷大阻抗,可将增益推至接近gm·ro的理论极限;二极管连接负载则以牺牲增益为代价,换取线性度与稳定性。例如,在差分放大器中,采用PMOS有源负载可规避体效应,使增益突破1000倍(60dB)。

应用场景:从电源管理到AI芯片

本征增益的优化直接影响电路性能。在电源管理芯片中,高本征增益的MOS管可提升LDO(低压差线性稳压器)的环路稳定性;在AI芯片的模拟前端,低噪声、高增益的MOS管能增强传感器信号的信噪比;而在5G通信中,本征增益与特征频率的权衡,直接决定了功率放大器的效率与带宽。

未来趋势:新材料与新结构的突破

随着GaN、SiC等宽禁带材料的兴起,MOS管的本征增益有望通过降低沟道电阻、抑制短沟道效应实现质的飞跃。同时,超结MOS、FinFET等新结构通过优化电场分布,进一步拓展了增益与速度的兼容空间。